eCADSTAR e il TDR nell’hardware e nella simulazione

Il TDR esiste da molto tempo. È attrezzatura standard per molti ingegneri, compresi gli installatori di telecomunicazioni e di banda larga domestica. L’analisi TDR in eCADSTAR’s Signal Integrity Advanced crea risultati simili ad un TDR con simulazione.

L’harware TDR

Un giorno a Glasgow, molto tempo fa, il mio collega Dugald mi condusse in un laboratorio laterale pieno di attrezzature e un groviglio di cavi. Dugald aveva costruito il suo kit da radioamatore e lo usava per “chattare” con altri radioamatori di tutto il mondo. Ero nuovo e in soggezione per le sue capacità.

“Cosa pensi che faccia questo?” mi chiese, gesticolando verso una grande scatola blu con un sacco di manopole e uno schermo.

“Oscilloscopio?” Risposi.

Lui scosse la testa e indicò due spezzoni di coassiale, uniti da un connettore a Y, che penzolavano dal pannello frontale. “Cosa pensi che stia succedendo qui?”.

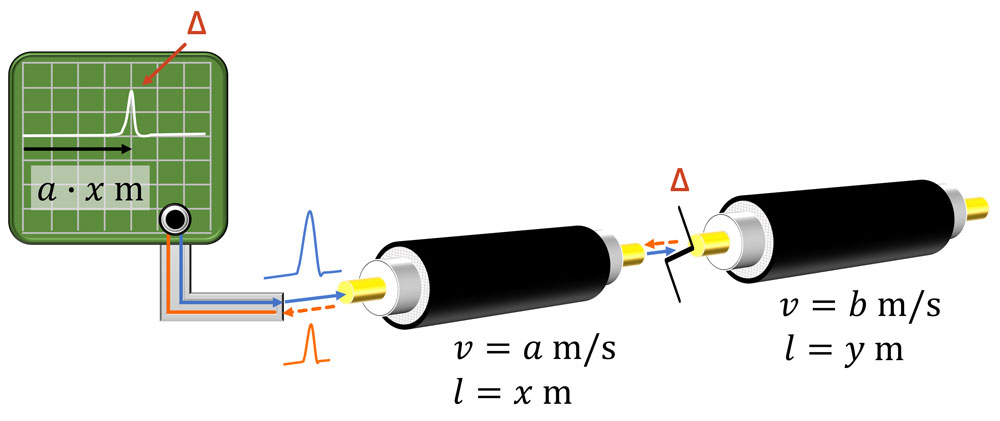

Un po’ come la disposizione della Figura 1.

Avevo pensato che i cavi penzolanti fossero stati lasciati lì quando qualcosa era stato scollegato, così gli dissi.

Indicò lo schermo e un puntino sulla traccia. “Quello è il connettore”.

Fu allora che imparai come le discontinuità causano riflessioni e come, se si sapeva quanto velocemente un’onda stava viaggiando lungo un cavo, si poteva dire dove erano. Si invia un impulso lungo il cavo – come un esploratore. Colpisce la discontinuità e una parte di essa torna indietro per dirti dove si trova. Potete vedere cosa succede nella figura 2. A condizione che tu sappia quanto velocemente viaggia l’impulso – e questo è prevedibile con un buon coassiale – il tempo che impiega il segnale a raggiungere la discontinuità e a riflettersi al TDR dà la sua posizione.

Il mese scorso, un tizio dei telefoni è venuto da noi per montare un nuovo hub a banda larga. Il nostro è ancora in rame fino alla scatola dove passa alla fibra. Quando ha staccato il vecchio hub, ha testato la linea con un TDR portatile. È una fortuna che l’abbia fatto, perché ha mostrato un piccolo difetto che deve aver rallentato la vecchia connessione per anni. Qualcuno aveva probabilmente ammaccato il cavo con una vanga da giardino – forse ero io. Il TDR ha inchiodato la dimensione della discontinuità e la sua posizione.

TDR analisi in eCADSTAR

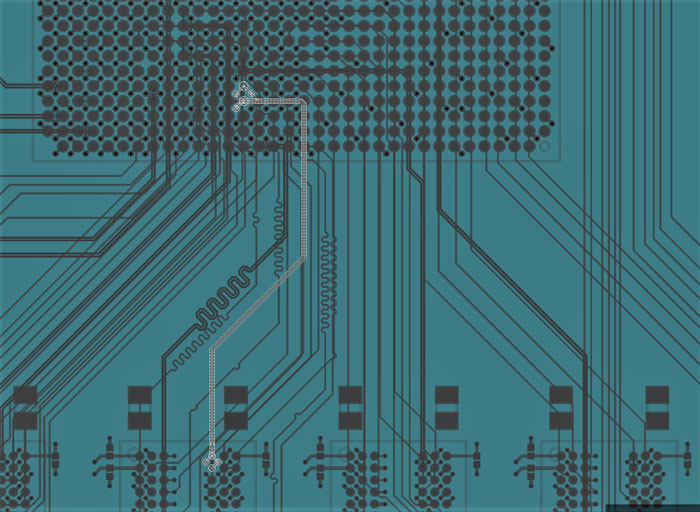

Le discontinuità sui PCB possono essere sottili – comprese le interruzioni nei piani di riferimento e gli errori nella spaziatura da traccia a traccia. Ma molte cose alterano le forme d’onda. Come puoi distinguere gli effetti di discontinuità dagli altri? Come puoi localizzarli esattamente e vedere quanto sono gravi?

L’analisi TDR si concentra specificamente sull’interconnessione – localizzando discontinuità inaspettate e vedendo se sono abbastanza grandi da essere importanti. Le impostazioni rispecchiano quelle che faresti su un TDR hardware.

Puoi usare gli stessi modelli della simulazione standard o impostare il tuo segnale a impulsi o a step e testare le condizioni.

Esempio

Il modo migliore per vedere cosa rende la simulazione TDR degna di essere fatta è di usarla come l’hardware che Dugald mi ha mostrato in laboratorio. Il TDR diventa il nostro generatore di segnali, l’impedenza della sorgente e l’impedenza di carico. Ora stiamo guardando la qualità dell’interconnessione e solo quella.

Il segnale è una linea differenziale DDR4 byte lane strobe.

Molte cose possono accadere sulla strada dal controller alla SDRAM e la simulazione TDR rende il controllo molto più facile.

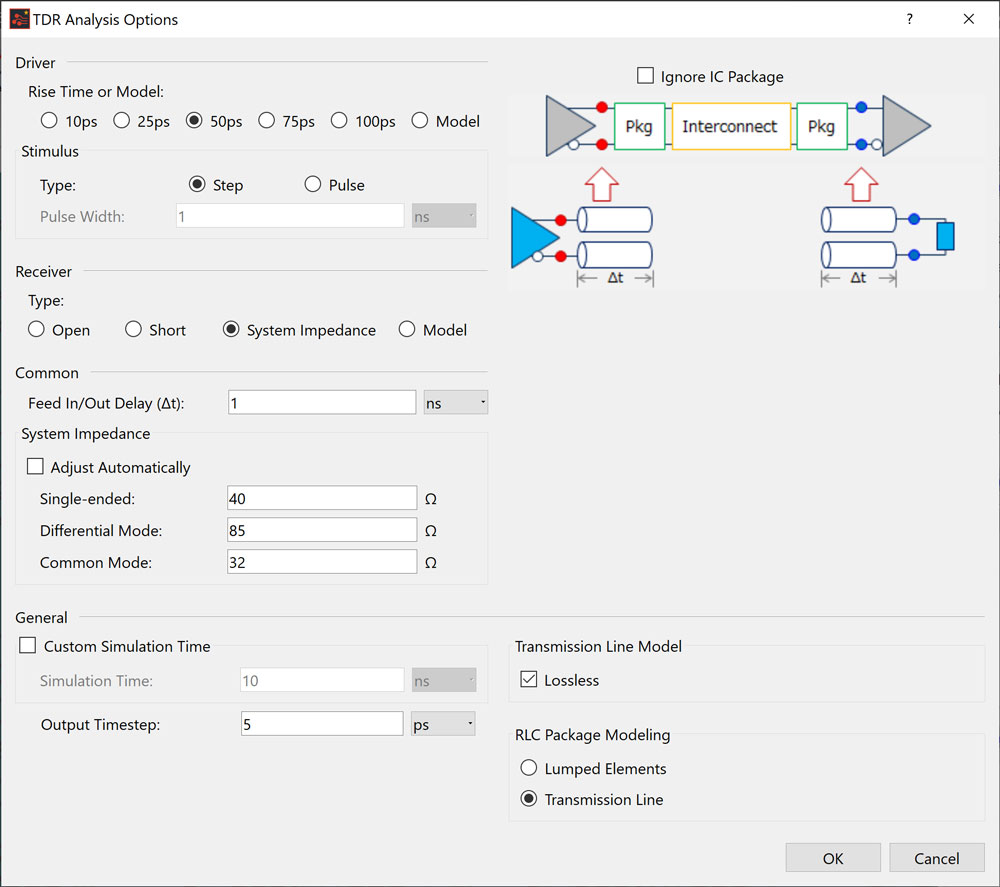

Impostiamo un’analisi TDR (Figura 5). Questo tipo di memoria ha tempi di salita veloci. In ogni caso, tempi di salita veloci su uno stimolo troveranno glitch più sottili di quelli lenti. Voglio scegliere un tempo di salita che il mio TDR hardware possa gestire se ho bisogno di confrontare i risultati. Ho scelto un semplice stimolo a passi con un tempo di salita di 50ps.

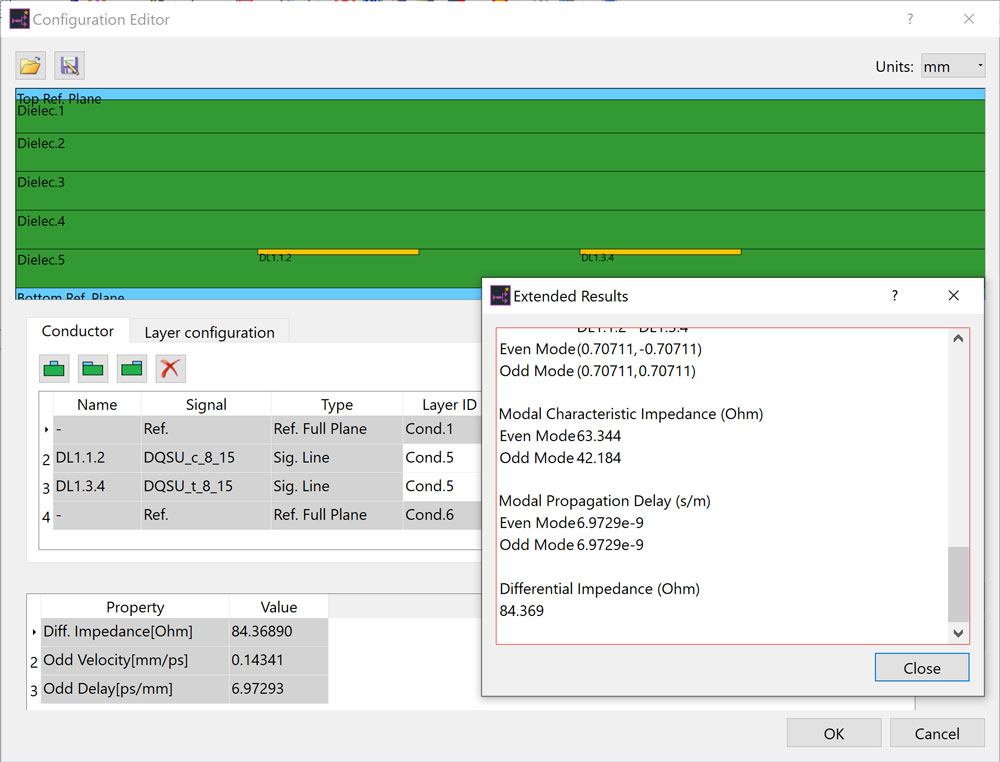

Ho scelto di ignorare i modelli di simulazione tranne che per le parassitiche del pacchetto e collegare entrambe le estremità all’impedenza del sistema. Nel caso vi stiate chiedendo da dove ho preso queste impedenze single-ended, modalità differenziale e modalità comune, corrispondono ai valori previsti nel routing. Ho creato uno scenario in Electrical Editor e ho risolto la configurazione di traccia prevista (Figura 4). I risultati non mostrano direttamente un valore di modo comune, ma è possibile ottenerlo dividendo l’impedenza di modo pari per due. Ho giocato un po’ grossolanamente con la precisione, ma potete sperimentare con i valori di impedenza, specialmente quando si tratta di modalità. La differenza tra i valori di modo dispari e single-ended dipende molto dall’accoppiamento differenziale e dalla distanza dal piano di riferimento più vicino.

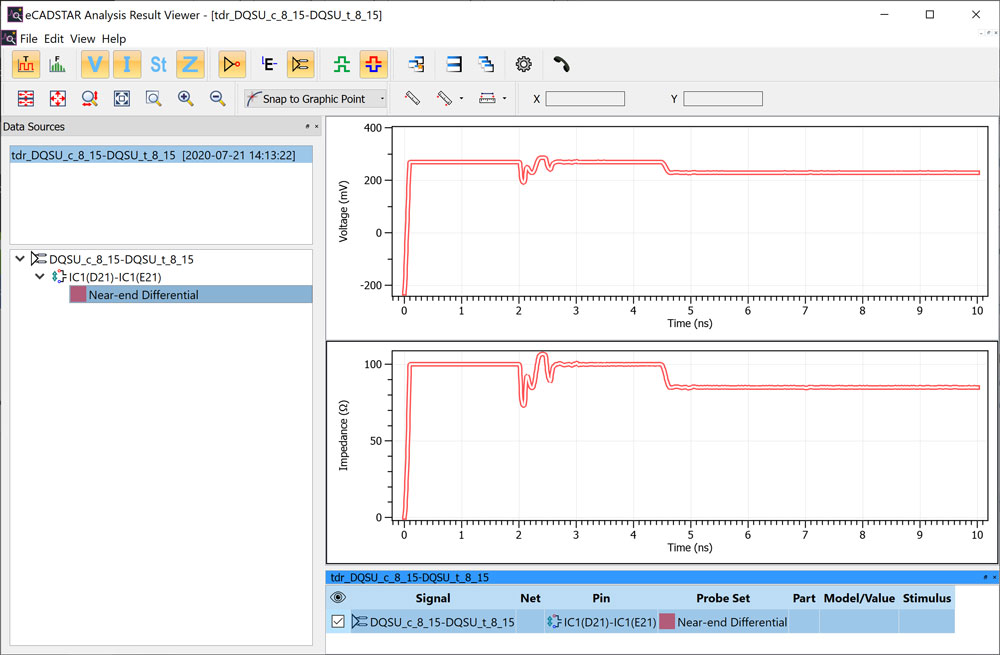

I risultati sono presentati nello stesso modo della simulazione standard, con la stessa ricchezza di opzioni, ma voglio solo parlare di quelle più ovvie. Il grafico superiore è la tensione e quello inferiore l’impedenza differenziale. C’è un bel guasto a partire da 2ns. Nella Figura 5, potete vedere che ho impostato il ritardo di entrata/uscita a 1ns. Il tempo di andata e ritorno per questo è 2ns, che è dove inizia il glitch, quindi qualcosa sta accadendo vicino alla fine del controller del routing.

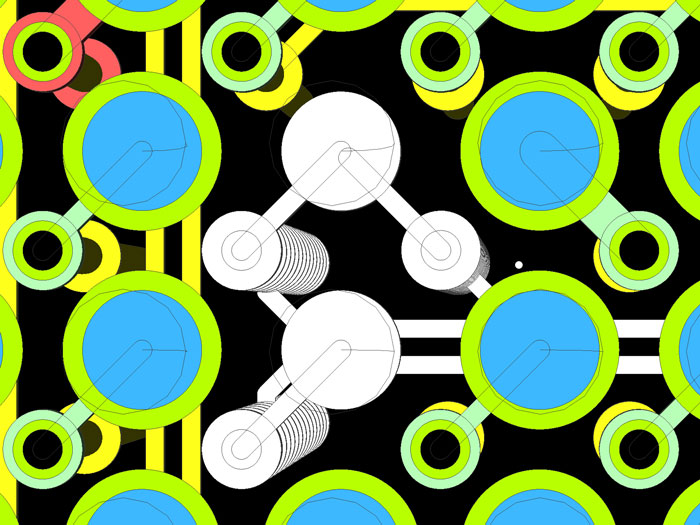

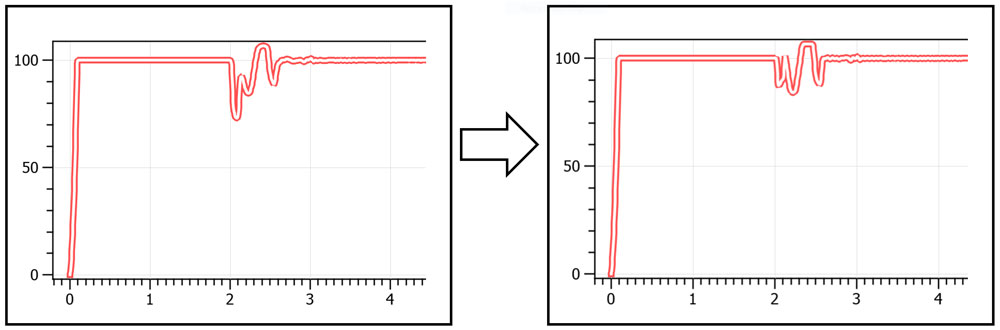

Ingrandendo, potete vedere che ho fatto un errore nel fan-out dal controller, aggiungendo un ulteriore via di fan-out su un lato della coppia (Figura 7). Se non avessi disattivato la rimozione automatica degli anelli durante il routing, non sarebbe successo.

Quando tolgo la via extra e lo stub, c’è ancora una discontinuità sulla transizione da fan-out a pair routing, ma molto più piccola (Figura 8)

Una considerazione finale sull’analisi TDR

Mi piace l’analisi TDR perché il setup è autonomo. Si può fare senza riferimento ad altri modelli e setup, ed è facile da collegare all’hardware. Puoi controllare l’interconnessione ad alta velocità da sola, eliminando altri fattori che possono rendere più difficile collegare causa ed effetto. E se si usano anche i TDR dell’hardware, i loro risultati sono facililmente relazionati ai risultati dell’analisi TDR di eCADSTAR.

Informazioni sull'autore

-

Jane Berrie•Signal Integrity Expert, Zuken Tech Center, BristolJane Berrie è coinvolta in EDA per l'integrità del segnale PCB dagli anni '80. I suoi articoli sono apparsi in molte pubblicazioni in tutto il mondo - troppe volte per poterli citare. Jane è anche presidente della sessione passata per la progettazione di circuiti integrati 3D alla conferenza annuale di automazione della progettazione. Jane è anche un'innovatrice con una prospettiva unica, che lavora costantemente a nuove soluzioni nel mondo in rapida evoluzione della progettazione elettronica. Nel suo tempo libero, Jane ha organizzato eventi di beneficenza a tema - tra cui due a favore delle scialuppe di salvataggio e della sopravvivenza dello scoiattolo rosso. Jane è anche una frequentatrice abituale della discoteca.