Im Paket enthalten

✔ Step I/O

✔ Zugang zu Online-Bauteilanbietern

✔ Lizenzausleihe (nur in der Version Netzwerk)

✔ Step I/O

✔ Zugang zu Online-Bauteilanbietern

✔ Lizenzausleihe (nur in der Version Netzwerk)

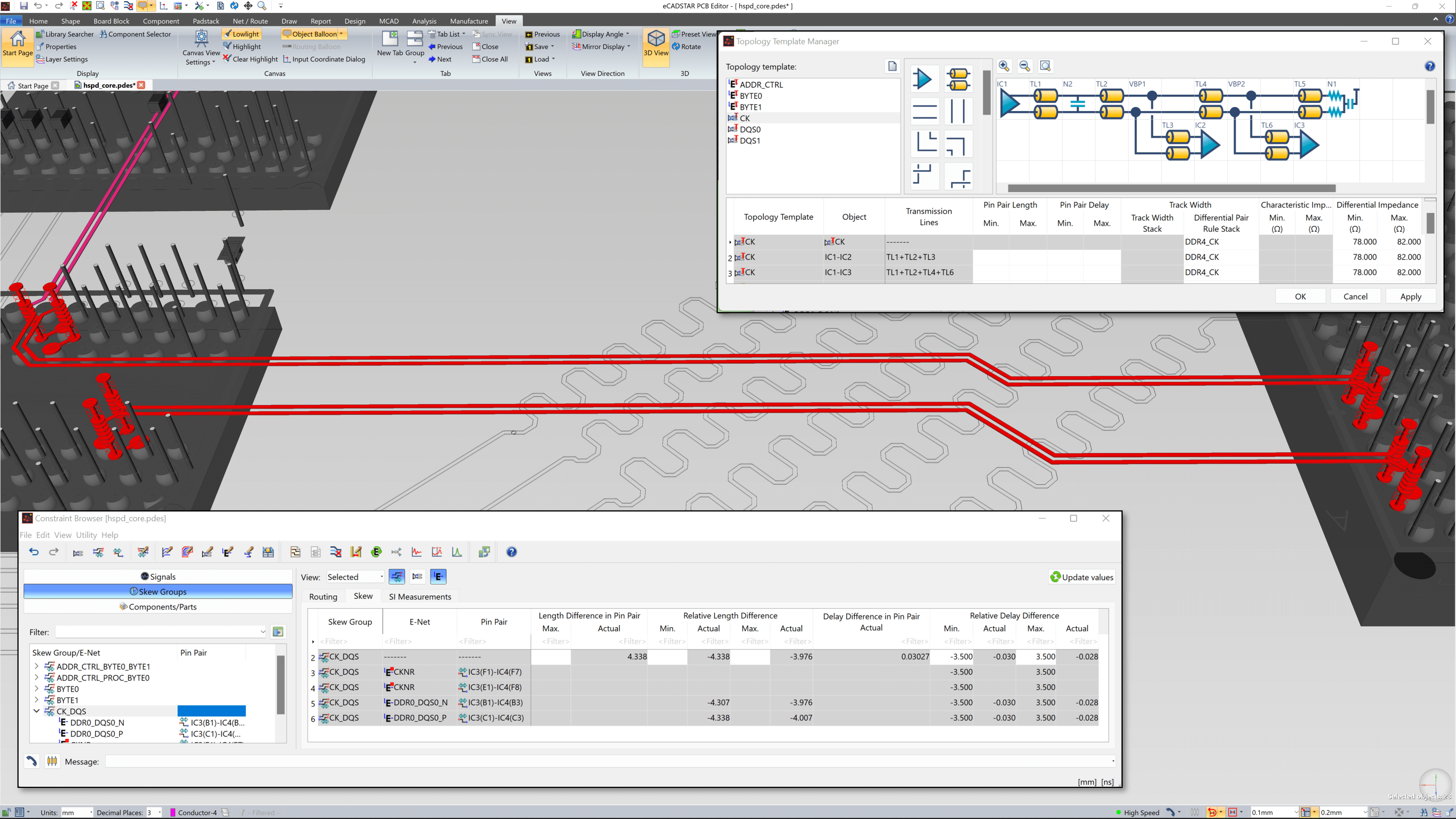

Selbst wenn der größte Teil Ihrer Leiterplatte z. B. aus analogen oder digitalen Schaltungen mit geringer Geschwindigkeit besteht, kommen häufig High-Speed Komponten zum Einsatz, die eine Topologiekontrolle erfordern. Moderne Leiterplatten sind selten vollständig „Low-Speed“ oder „High-Speed“.

High-Speed-IO ist bei vielen gängigen Geräten Standard. DDR4-Speicher ist layoutkritisch, auch wenn er relativ langsam läuft. Das Gleiche gilt für gängige Busse wie PCI Express oder USB Typ-C. Sogar DC/DC-Abwärtswandler (Abwärtswandler) sind hochgeschwindigkeits- und layoutkritisch, da im Gegensatz zu älteren linearen Wandlern Teile ihrer Schaltung mit hohen Frequenzen laufen.

Für eCADSTAR ADVANCED HS sind weitere optionale Extras verfügbar. Sie können Autorouting oder Gerber-Import wie bei BASE hinzufügen, aber Sie können auch aus einer Reihe von fortgeschrittenen und vollständig integrierten Funktionen wählen, die Ihnen helfen, das High-Speed-Design zu optimieren. Hier sind sie:

All diese Ansichten sind beim Design von High-Speed-Schaltungen unerlässlich, so dass Sie mit eCADSTAR stets die volle Kontrolle und Sichtbarkeit haben.

So wurden z. B. relative Skew-Constraints zwischen differentiellen Byte-Lane-Strobes und der Clock festgelegt, die für kontrollierte Topologie und Impedanz konfiguriert sind.

Sie können die Einstellungen jederzeit aufrufen und anpassen und die Ergebnisse sofort überprüfen, um Ihre Leiterplatte auf bestmöglich abzustimmen.“