EMBEDDED SIGNAL INTEGRITY ANALYSIS

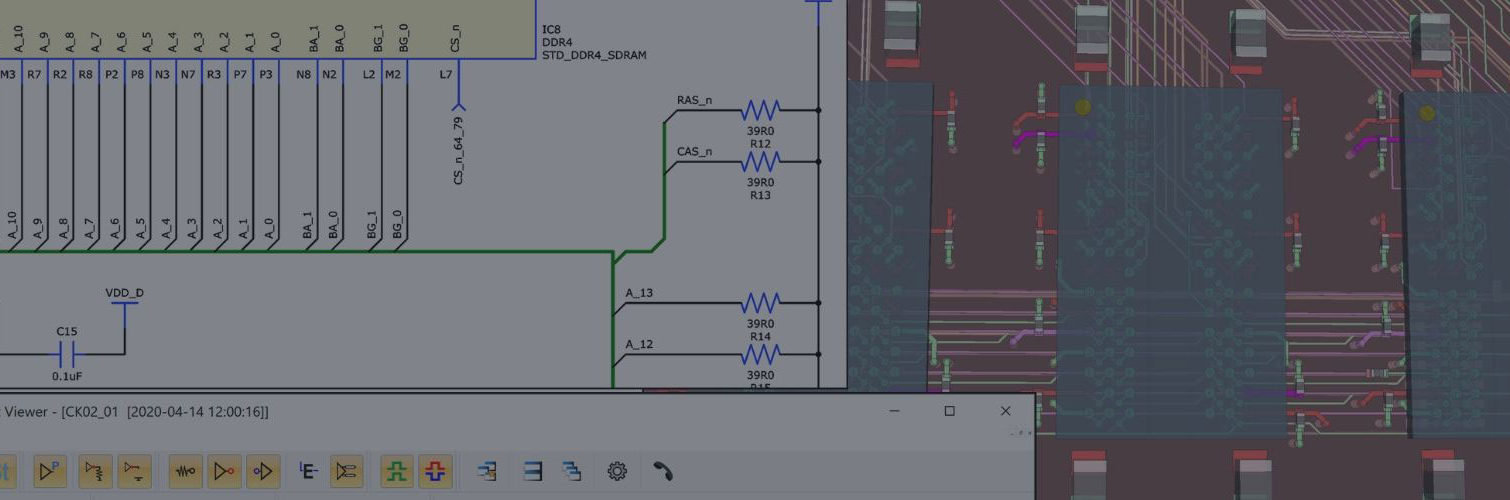

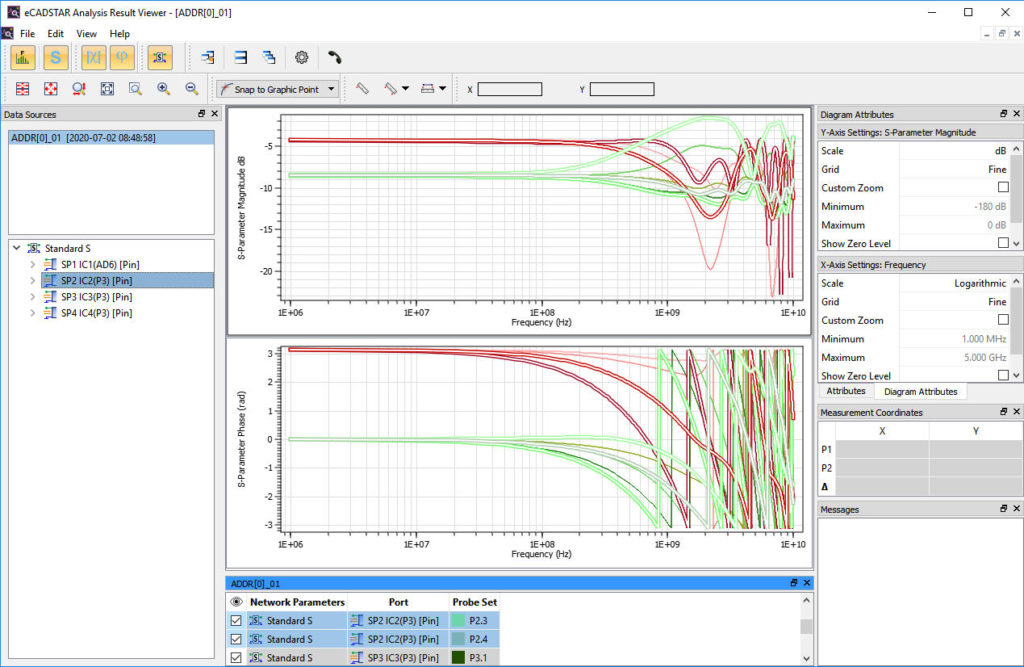

Signal integrity analysis is embedded into the eCADSTAR Schematic and PCB Editors providing pre-layout and post-layout simulation capabilities.

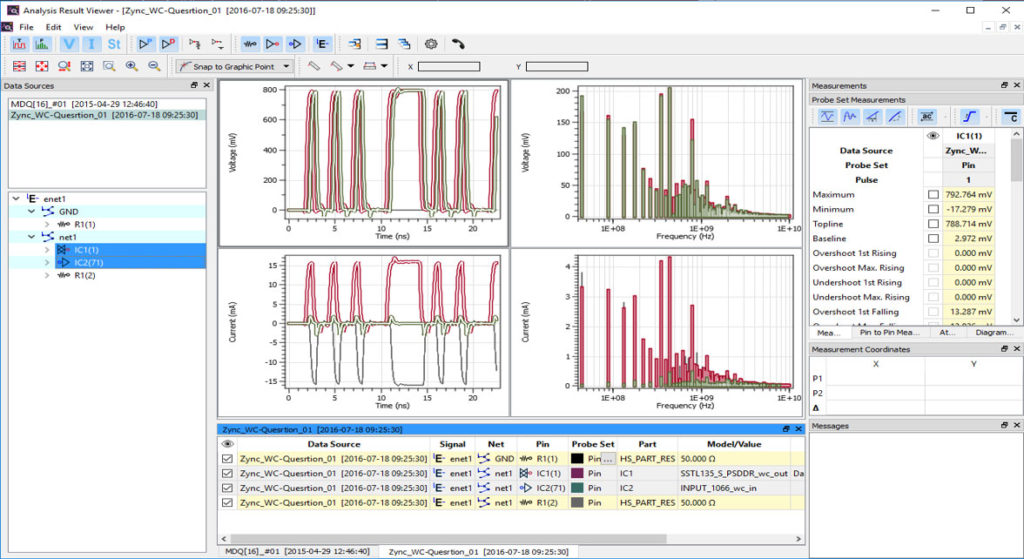

- Simulate, measure, share results independently of PCB design.

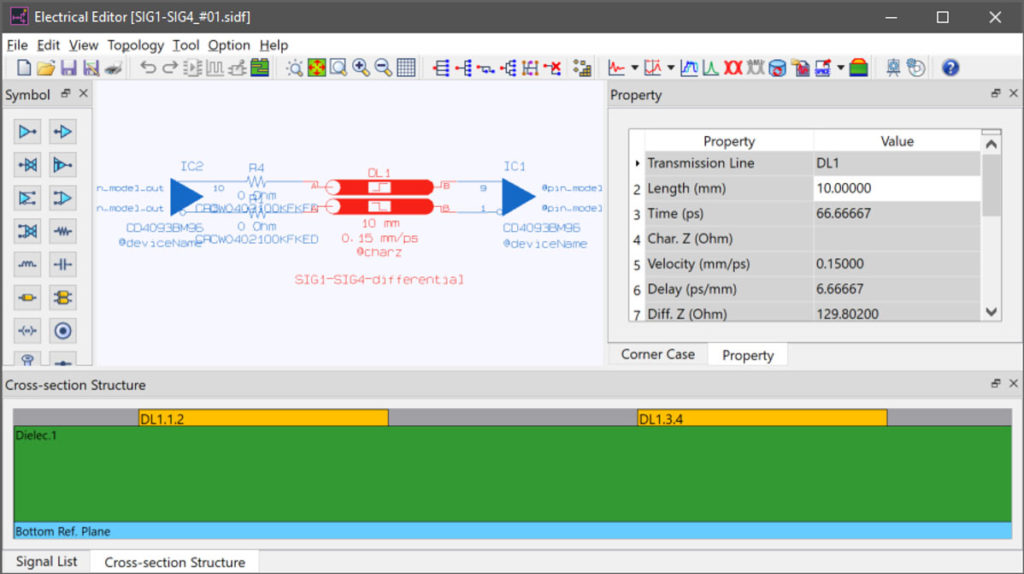

- Constrain and plan topologies in the pre-layout phase.

- Plan impedance using the integrated field solver using lossy interconnect models.

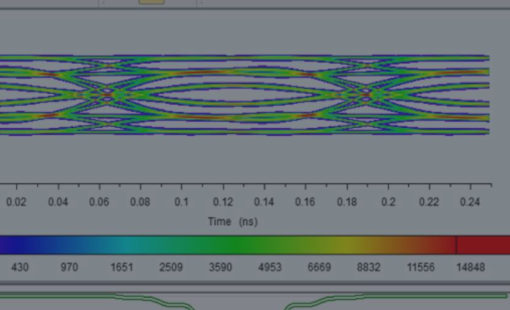

- Analyze signals in the time domain.

- Automatic measurement for key distortion and timing parameters (e.g. slew rate) allows fast error detection.